DACにオーディオデータを流し込むのに使われてるI2Sインタフェース、実際に流れている信号を、ロジック・アナライザでキャプチャーしてみた。

DSDが本当にDSDで渡っているのか、見た目や聴感でわからないから、よーし、見てやればスッキリするだろうという、安直なきっかけ。

構成

構成は、過去記事で紹介してる機材の組み合わせ

このロジアナの分解能が24MHzなので、同期クロックは丸められて、表示上等間隔にならないタイミングがあります。信号が乱れてるわけではない(はず)です。

キャプチャしてみる

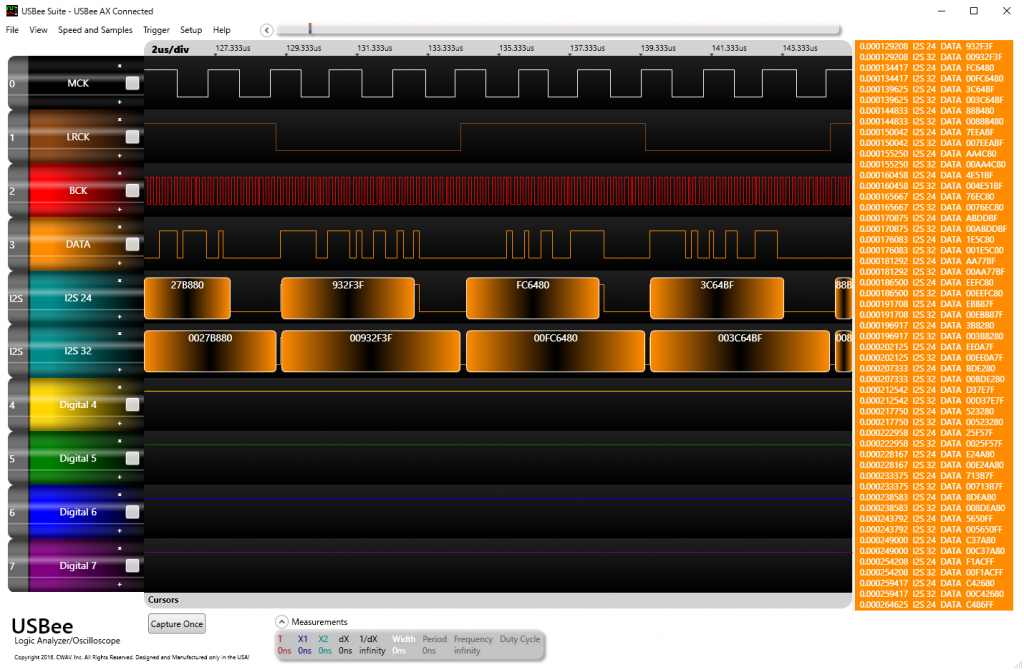

・PCM 96KHz/24bit

わかること

- BCKが同期クロックで、その立ち上がりエッジでDATA見るんだな

- 32ビットごとにLRCKで左右切り替えてるんだな

- DATAの音源24ビットでも、32ビットで空き0埋めなんだな

- MCK?!一瞬綺麗なクロックに騙されかけたけど、そもそもこのロジアナの分解能では飽和(本当はもっとONOFFしてるが追いつかないので取り逃してる)してるので嘘表示です。参考にもならないんだな。(´・ω・`)

※このDAC構成ではMCKは使ってません。DDCからは出てくるので拾ってるだけ。

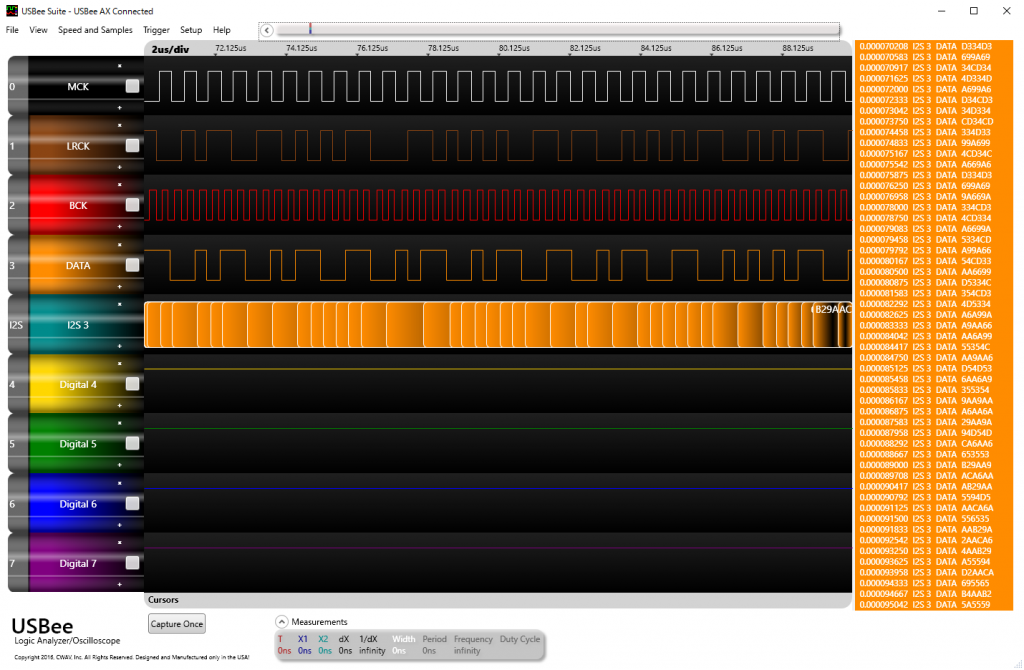

・DSD64

わかること

- LRCKとDATAに1ビットストリームが流れるんだな

どっちかが左(DSDL)で、どっちかが右(DSDR)なんだろうな - BCKが同期クロックなのはPCMと同じなんだな

- MCK・・げふげふぅ(参考にもならない参考)

- すっげぇ、単純なんだな

まとめ

信号も実際に目で見るとわかりやすい。

ちゃんと、DSDはDSDで渡ってることがわかって満足。

感想としては、予想以上にシンプルな手順と思った。双方向じゃないし。

DSD、ちょっとした回路でDA変換できるって聞くけど、わかる気がする。しかしDSDはLRCKとDATAに左右載せるって、何かで定義されてるのだろうか。

あと、マスタクロックちゃんと把握したかったな。

DSD128やPCM192KHzもキャプチャしたんだけど、BCK単純に倍になって飽和しはじめて、定期的に2クロックが1クロックにひっつきはじめた。アナライザの解析も狂うので、そういう比較記事も載せたかったけど、割愛しました。

100MHzぐらい分解能あれば、形はどうあれ取りこぼしなしでいけるかな。でも、このために、買うのももったいないか。

Aliexpress除くと、30ドルぐらいである。うーーーん。(´・ω・`)

ピンバック: DACほんとに自作してみた – ちょこビット